Introducing Blaze

At Ingonyama, we are developing FPGA acceleration solutions for common ZK primitives with the goal of making FPGA acceleration as developer friendly as GPU acceleration.

To this end, we introduce Blaze, a Rust library for ZK acceleration on Xilinx FPGAs. Our goal with Blaze is to make FPGA acceleration accessible to ZK developers.

What is Blaze?

Blaze is a Rust library that allows access to Ingonyama’s implementation of primitives such as MSM, NTT, and Poseidon hash on an FPGA, without much hassle or overhead. Blaze will abstract away the complexities of reading/writing from FPGAs and flashing FPGAs.

It is also possible to use Blaze with your own FPGA programs. However, you will need to define your own configuration as well as implement a client.

Currently, we support the C1100/U55C Xilinx FPGA card.

Who is Blaze for?

Blaze is for anyone who requires high-performance ZK primitives in their application.

We envision Blaze being used by protocol developers and proof providers wanting to upgrade existing protocols with FPGA acceleration for increased performance.

What problem is Blaze trying to solve?

Before Blaze, when your team would want to design an FPGA and write software integration for it, the software development team would have to be very knowledgeable regarding interfacing with FPGAs and would need to write its integration logic at the Driver level.

Blaze now allows the software team to simply get a configuration file from the Hardware team and interact with the high-level Blaze API.

Blaze — architecture overview

Blaze is a library for interacting with FPGAs (DriverClient in the diagram). Blaze implements low level methods for interacting with the XDMA and other parts of the FPGA. Blaze allows developers to define FPGA APIs in the form of JSON objects, from these, we may generate clients that implement high-level easy-to-use drivers.

We can combine Blaze with our Driver Manager (future feature release). The Driver Manager keeps a pool of DriverClients representing the existing FPGAs on the machine. Applications communicate with the Driver Manager by sending requests in the form of data written to shared memory and a payload with request details. The Driver Manager will then orchestrate the task requests between available FPGAs Blaze clients according to availability and task load.

Getting Started with Blaze

Before we dive into the Blaze API, we would like to provide an overview of some basic FPGA concepts and terminology. Though it’s not necessary to be familiar with this terminology to use Blaze out of the box, we think it’s important to understand the protocols and interfaces Blaze is abstracting away.

What is an FPGA?

Field Programmable Gate Arrays (FPGAs) are semiconductors, but unlike other integrated circuits such as ASICs, you can think of an FPGA as a clean slate. It is as close a developer can get to designing custom hardware, without actually needing to manufacture anything. Out-of-the-box FPGAs don’t do anything at all but can be programmed to do anything you wish. They are also nearly stateless; the moment you switch them off they are reset.

In general, FPGAs have three main components:

- Logic cells

- Interconnects

- IO blocks

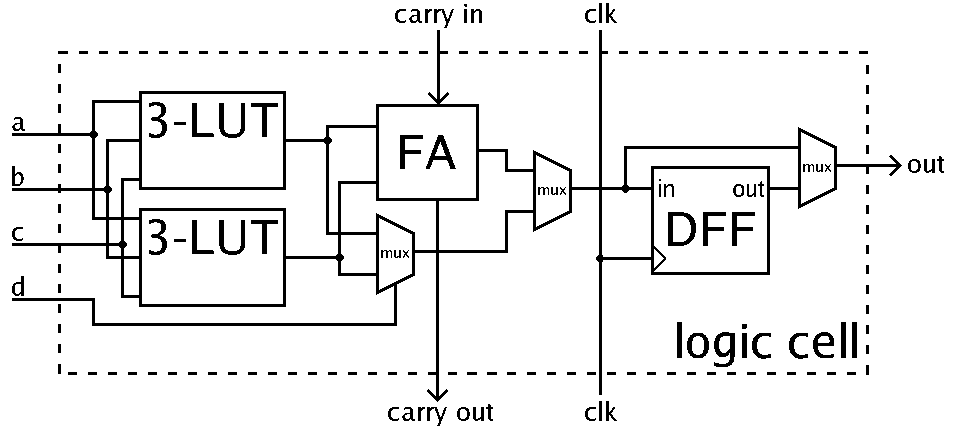

A TL;DR of these components is that logic cells are state machines allowing you to define your program. A logic cell is constructed of lookup tables (these act as RAM for combinatorial logic functions), flip-flops for storing state information, and multiplexers these route logic between elements of the block and external resources as well.

Interconnects connect the Logic cells and route data between them, and IO cells allow the FPGA to read and write to the outside world via different interfaces. All of these components can be programmed with DSL languages; one example would be Verilog.

We will now briefly touch on some of the main components used in an FPGA environment, just to solidify a high-level understanding.

IP Cores

IP cores are “modules” designed and tested by 3rd party companies such as AMD / Xilinx or another team member. These modules come in both software and hardware form and offer thoroughly tested solutions for common challenges FPGA designers may encounter.

AXI

The AXI (Advanced eXtensible Interface) is a communication protocol used primarily within FPGAs, ASICs, and SoCs (System-on-Chip) for facilitating communication between different components, such as processor cores, memory controllers, and peripherals. AXI is part of the AMBA (Advanced Microcontroller Bus Architecture) family of protocols, which is developed by ARM. You can think of AXI as an efficient internal communication protocol helping the FPGA’s inner components speak with each other.

HBM

High Bandwidth Memory (HBM) is a high-performance memory technology that is integrated closely with the FPGA to provide high memory bandwidth and low power consumption. HBM is particularly useful for applications that require large amounts of data to be processed quickly (MSM for example).

HBM is an actual physical component in the FPGA; uses 3D-stacked memory architecture, delivering superior performance than traditional DDR RAM. The HBM memory controller, usually a hard IP core, uses AXI to communicate with other components in the FPGA.

DMA

DMA (Direct Memory Access) allows for data transfer between external devices and the FPGA without the need for a processor to be involved (DMA can also facilitate internal data transfer between FPGA components).

Xilinx provides an IP Core called XDMA (Xillinx DMA). XDMA is specifically designed for high-performance data transfers between the FPGA and the host system over the PCIe (Peripheral Component Interconnect Express) interface.

HBI

The Host Bus Interface in an FPGA serves as the interface, or bus, that connects the host system to the FPGA, enabling communication, control, and data transfers between them.

Introduction to Blaze

Blaze is our solution for developer-friendly FPGA integration. Blaze abstracts away the complexities of interacting with an FPGA and provides developers with a simple and composable way to build FPGA-accelerated applications.

Blaze also makes it easy for developers to define application-specific clients (or use Ingonyama clients), which can easily harness the power of Ingonyama’s FPGA solutions for many of the most important ZK primitives.

FPGAs can be pooled together to perform a specific task, or each can run its own program individually. Blaze is stateless at the moment, however, we are working on a management layer that can be used to seamlessly orchestrate multiple devices.

To learn how to set up a project and use Blaze, read the full article on Medium or visit the Blaze Github.